1奈米晶片在2027年實現?

2021/12/03

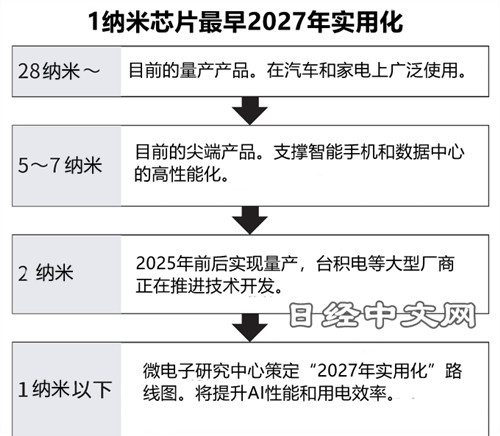

全球尖端半導體的開發競爭將進入新階段。與世界大型企業展開合作的比利時研究機構微電子研究中心(imec)策定了電路線寬為1奈米(奈米為10億分之1米)晶片在2027年實現實用化的路線圖。表示之後的0.7奈米晶片也將在2029年以後量産。如果成功實現,人工智慧(AI)等的處理性能有望飛躍式提高。

尖端半導體在約50年裏維持符合性能約2年翻一番的「摩爾定律」的技術開發。近年來,有觀點認為臨近物理極限,但微電子研究中心的首席執行官(CEO)Luc Van den hove接受日本經濟新聞採訪時強調:「(摩爾定律)將隨著與新技術的結合而持續」。

微電子研究中心是擁有約5000名研究者的非營利的研究機構。台積電(TSMC)、美國英特爾和南韓三星電子等大型半導體廠商、設備與原材料廠商通過派遣研究人員或進行委託研究來參與其中。此前,根據微電子研究中心的路線圖開發的技術成為各企業推進實用化的基礎。

|

此次,微電子研究中心提出新的路線圖,在預測尖端半導體今後的發展方面成為重要指導方針。

受此推動,今後著眼於「1奈米以下」的競爭或將全面啟動。目前的尖端産品為台積電和三星量産的5奈米晶片,兩家企業計劃在2025年啟動2奈米晶片的量産。英特爾也表示,同一年恢復世界頂尖的製造技術,正加快推進研發。美國IBM於5月宣佈已成功進行2奈米晶片的試製。

此前開發競爭的核心是電路線寬的微細化,但Luc Van den hove指出,今後除了微細化之外,「通過新元件結構以及將電晶體與晶片堆疊起來的三維化,(性能提高)將被實現」。關於新結構等的實現,對於和日本材料廠商的合作顯示出期待。

|

| 微電子研究中心的首席執行官(CEO)Luc Van den hove |

另一方面,關於2奈米以下量産不可或缺的新一代EUV(極紫外)光刻設備,正在與荷蘭ASML控股推進共同開發項目,日本東京電子也參與其中。Luc Van den hove針對項目的進度透露,「計劃到2023年初推出試製機,還有企業尋求2026年實現量産」。

半導體性能的飛躍式提高將在家電和機器人等日常生活中的「邊緣終端」領域推動負責計算處理的AI的利用。現在,AI的龐大計算處理在雲平臺上完成的情況很多,但Luc Van den hove指出,「未來將變為(與邊緣終端)保持平衡」,隨著處理由雲平臺和邊緣終端分擔,希望有助於減少向數據中心發送之際等需要的耗電量。

日本經濟新聞(中文版:日經中文網)龍元秀明

版權聲明:日本經濟新聞社版權所有,未經授權不得轉載或部分複製,違者必究。

報道評論

HotNews

金融市場

| 日經225指數 | 56941.97 | -697.87 | 02/13 | close |

| 日經亞洲300i | 2681.80 | -15.65 | 02/13 | close |

| 美元/日元 | 152.73 | -0.27 | 02/14 | 05:50 |

| 美元/人民元 | 6.9077 | 0.0080 | 02/13 | 17:40 |

| 道瓊斯指數 | 49500.93 | 48.95 | 02/13 | close |

| 富時100 | 10446.350 | 43.910 | 02/13 | close |

| 上海綜合 | 4082.0726 | -51.9451 | 02/13 | close |

| 恒生指數 | 26567.12 | -465.42 | 02/13 | close |

| 紐約黃金 | 5022.0 | 98.3 | 02/13 | close |